新聞資訊

隨著芯片制造業面臨提升處理器性能的新挑戰,因不斷增加晶體管密度變得愈發艱難,企業開始尋求替代策略,包括架構革新、擴大單片芯片尺寸、采用多芯片設計方案以及發展如 Cerebras WSE 系列那樣的晶圓級芯片。

近期,中國科學院計算技術研究所的研究人員發布了一款基于 RISC-V 架構的創新性設計——一款擁有 256 核心的多芯片組合,并計劃將其拓展至包含 1,600 核心的單片晶圓規模芯片。

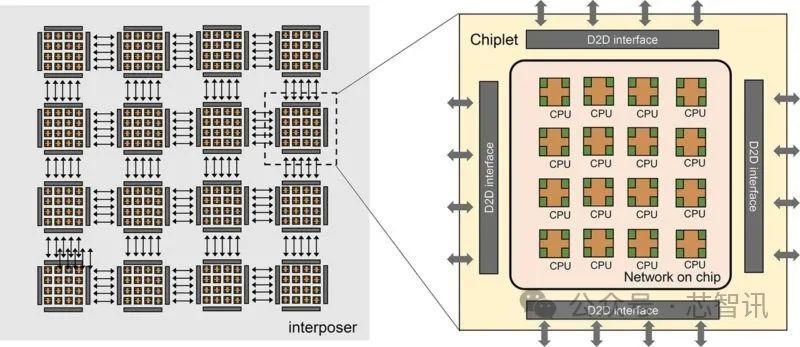

據 The Next Platform 報導,中國科學院計算技術研究所的科研團隊在最新一期《基礎研究》期刊上公開了一項成果——名為“浙江大芯片”的256核多芯片計算平臺。此芯片設計由16個包含16個RISC-V內核的小芯片構成,借助片上網絡實現傳統SMP方式的資源共享。每個小芯片備有多種芯片間的互聯接口,能通過2.5D中介層與鄰近的小芯片相接,有望擴展至包含100個(即1,600個內核)的小芯片 ** 。

據悉,“浙江大芯片”采納Chiplet架構設計,并采用了22納米制程技術。盡管尚未明確在中介層互聯并在22納米生產節點上制造出1,600核心組件的具體能耗,但得益于延遲能力的降低,預期將會顯著改善功耗和性能表現。

文中還探討了光刻技術和Chiplet架構的局限性,同時指出此類新型架構對未來計算需求所具備的巨大潛力,尤其是在構建百億億次超級計算機處理器方面,AMD和Intel正積極投入此類技術研發。

研究人員提出:“對于當前乃至未來的百億億次計算,我們認為分層Chiplet架構將成為一種強有力且靈活的解決方案。它由多個內核及帶有分層互連的小芯片組成,在Chiplet內部,內核間的通訊依賴超低延遲互連,而在小芯片之間,則運用高級封裝技術提供的低延遲互連,這有助于最大程度地降低高擴展性系統中的小芯片延遲和NUMA效應。”

與此同時,研究者提醒,采用多級內存層次結構可能為這類設備的編程帶來復雜性問題。

論文描述:“內存層次結構包含了核心內存[緩存]、片內內存和片外內存。這三個層級在內存帶寬、延遲、功耗和成本上各有差異。在分層Chiplet架構的設計概念里,多個核心通過交叉開關相連并共享緩存,形成pod結構,多個pod通過Chiplet內網絡互聯形成一個Chiplet,多個Chiplet再通過Chiplet間網絡互連后連接到外部存儲器。要充分發揮這一層次結構的優勢,合理利用內存帶寬以均衡不同計算層次的工作負載,就需要精心設計通信網絡資源,從而確保Chiplet系統協同執行共享內存任務。”

此外,大芯片設計亦可結合光電計算、近內存計算和3D堆疊內存等先進技術。不過,論文并未詳述具體實施這些技術的細節,也沒有深入討論在設計與構建如此復雜的系統時所面臨的挑戰。

發布日期: 2024-03-25

發布日期: 2024-07-03

發布日期: 2024-05-17

發布日期: 2024-07-10

發布日期: 2024-06-03

發布日期: 2024-10-22

發布日期: 2024-07-17

發布日期: 2024-04-24

發布日期: 2025-05-19

發布日期: 2025-05-19

發布日期: 2025-05-19

發布日期: 2025-05-19

發布日期: 2025-05-19